# 2025 International Solid-State Circuits Conference

## (ISSCC) Review

광운대학교 전자통신공학과 채주형 교수

### Topic : Wireline (2)

#### Session 22 : Memory Interface

이번 ISSCC 2025의 Session 22는 Memory Interface의 주제로 총 5편의 논문이 발표되었다. 모두 한국에서 발표된 논문으로 22-2 논문은 HBM에서의 Quadrature Clock Distribution을 위한 주제이며, 나머지 4개의 논문은 모두 Single-Ended Multi-Level Signaling을 위한 다양한 아이디어를 제안하였다.

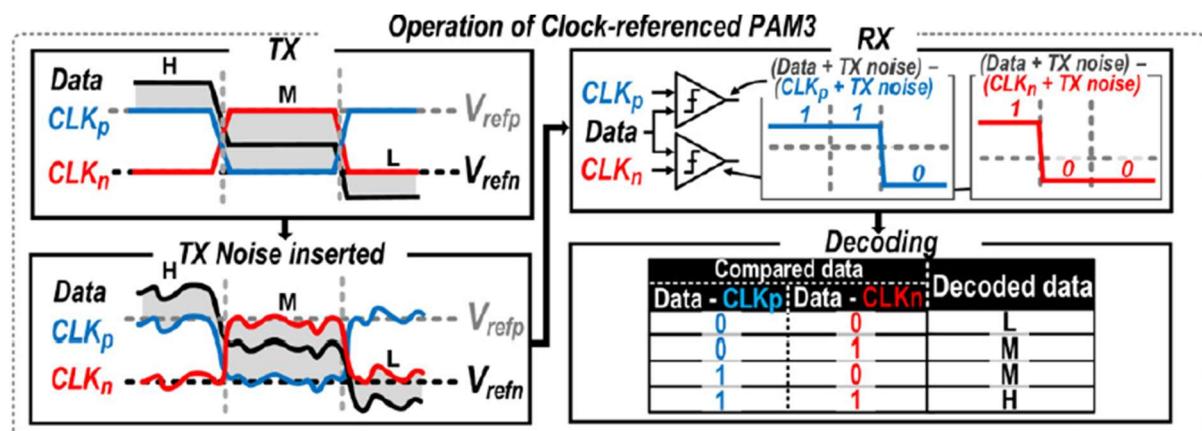

#22-1 SNU, 본 논문은 Chiplet과 Short-Reach Memory Interface를 위한 Clock-Referenced PAM-3 (CR-PAM3) Transceiver를 제안하였다. Single-Ended Signaling이 가지는 Voltage Reference (Vref) Offset과 TX/RX 간의 VDD와 Vref 노이즈 성분이 Uncorrelate되는 문제를 해결하기 위하여 Clock 신호를 RX의 Vref로 활용하는 방법을 제안하였다. 이와 함께 Far-End Crosstalk (FEXT) Cancellation 기법 또한 제안하였다. 이를 통해 Supply Noise가 있는 환경에서도 42 Gb/s/pin 속도에서  $10^{-12}$  이하의 BER 성능을 달성할 수 있었으며, 0.275 pJ/bit의 에너지 효율을 달성하였다.

[그림 1] 제안하는 CR-PAM3의 핵심 동작.

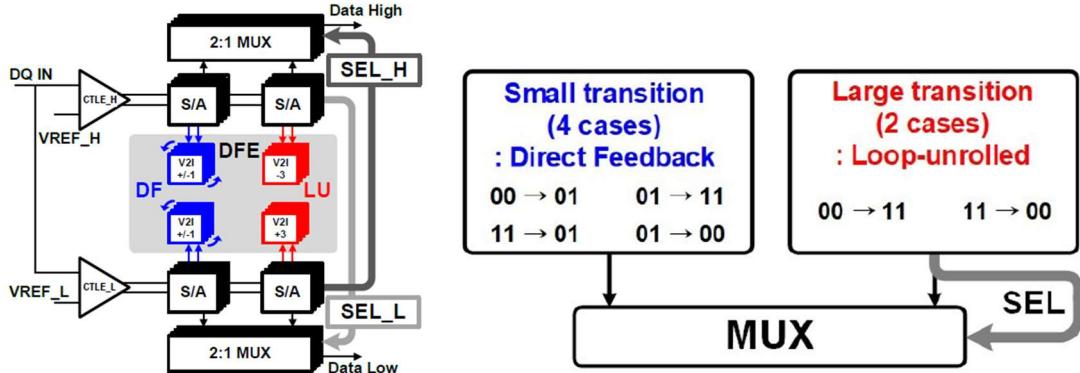

#22-3 SK Hynix, 본 논문은 Hybrid DFE가 적용된 GDDR7 PAM3 Receiver를 제안하였다. GDDR7은 PAM3 방식 적용과 함께 데이터 전송속도의 증가로 ISI를 제거하기 위한 DFE가 RX에 필요하다. 이 때 Direct DFE는 Feedback Time의 이슈가 있으며, Loop-Unrolled DFE는 파워 및 면적 증가의 이슈가 있다. 이를 해결하기 위하여 Short Transition에는 Direct DFE를 적용하고, Long Transition에

는 Loop-Unrolled DFE 적용하는 Hybrid DFE 방식을 제안하였다. 이를 통해 모두 Direct DFE만을 사용하는 경우에 비해 20%의 Feedback Time이 감소되었으며, -5 dB 손실의 GDDR7 채널 환경에서 42 Gb/s/pin의 데이터 수신성능을 달성하였다.

[그림 2] Hybrid-DFE PAM3 Receiver의 블록다이어그램과 동작 원리.

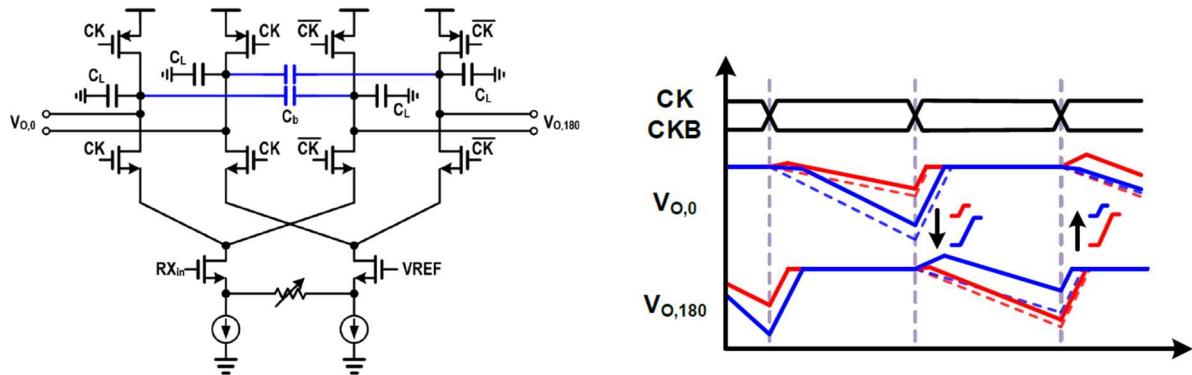

#22-5 Korea University, 본 논문에서는 Receiver DFE의 Feedback Time 및 파워/면적 문제와 Current Integrator의 Common-Mode Degradation 문제 등을 해결할 수 있는 Capacitive Feedback Equalizer (CFE)를 제안하였다. Current Integrator에 Capacitor를 결합하여 1-UI 이전의 데이터를 인가함으로써 Delay-less Equalizer를 구현하면서 Common-Mode 전압 또한 증폭시켰다. 이를 통해 0.3 pJ/bit의 에너지 효율로 32 Gb/s PAM4 데이터의 수신성능을 달성하였다.

[그림 3] 제안하는 Capacitive Feedback Equalizer의 동작 원리

### Session 36 : Ultra-High-Speed D2D and High-Performance Optical Tranceivers

이번 ISSCC 2025의 Session 36에서는 총 9편의 논문이 발표되었으며 이 중 3편의 Die-to-Die (D2D) Interface 논문과 6편의 Optical Interface 논문으로 구성되었다. 이 중 D2D Interface는 2편의 PCIe Advanced Package Link가 소개되었으며, 1편은 Edge Density를 늘리기 위한 Simultaneous Bidirectional Signaling 기법이 적용된 논문이 발표되었다. 3편 모두 Edge Density를 높이는 것에

초점이 맞추어져 있음을 알 수 있다.

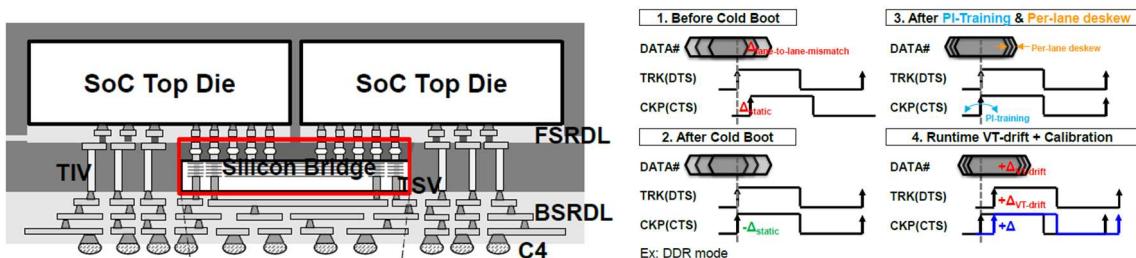

**#36-1 TSMC, 36-3 Cadence** 이번 ISSCC에서는 2개의 UCIe Advanced Package Link 논문이 소개되었다. TSMC의 경우 Dynamic Clock Gating을 적용하여 전력 소모를 감소시키면서 모드 변경 시점에서의 Voltage Droop 문제를 해결하기 위한 여러 방안들을 제안하였다. 이를 통해 64 Lane에서 32 Gb/s/pin의 특성을 달성하였으며, 또한 45 um의 Bump Pitch에서 10.5 Tb/s/mm의 Edge Density의 성능을 달성하였다. Cadence의 경우 CoWoS Packaging을 활용하였으며 이를 통해 16 Gb/s/pin의 전송 성능과 45 um의 Bump Pitch에서 5.27 Tb/s/mm의 Edge Density의 성능을 달성하였다.

[그림 4] UCIe System Overview와 RX Deskew Calibration 동작.

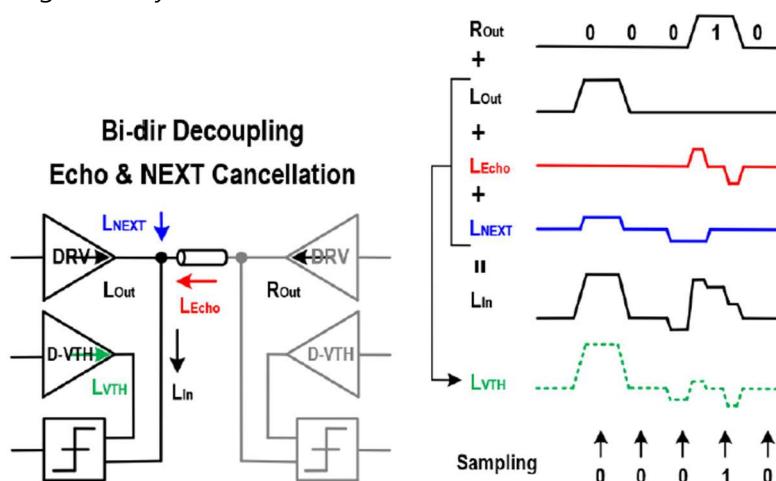

**#36-2 Peking University**, 본 논문은 D2D Interface의 Edge Density를 증폭시키기 위하여 Simultaneous Bidirectional (SBD) Signaling을 적용하였다. 채널간 피치가 작은 D2D Interface 환경에서 SBD를 적용하기 위해서는 Bi-Directional Coupling, NEXT, FEXT, 그리고 Echo 등의 노이즈를 줄여주는 것이 필요하며 본 논문에서는 이를 위한 방법을 제안하였다. FEXT의 경우 Capacitive/Inductive Coupling의 양이 동일하도록 채널을 디자인하여 노이즈의 영향을 최소화하였으며, NEXT, Echo 및 Bi-Directional Coupling은 Dynamic Voltage Threshold를 사용한 데이터 샘플링을 적용하여 문제를 해결하였다. 이를 통해 64 Gb/s/wire의 데이터 전송 성능을 달성하였으며 10.5 Tb/s/mm의 Edge Density 특성을 얻었다.

[그림 5] Dynamic Voltage Threshold를 이용한 SBD 데이터 샘플링.

## 저자정보

---

### 채주형 교수

- 소속 : 광운대학교 전자통신공학과

- 연구분야 : High Speed I/O, In-Memory Computing

- 이메일 : [jhchae@kw.ac.kr](mailto:jhchae@kw.ac.kr)

- 홈페이지 : <https://sites.google.com/view/jhchae>

-